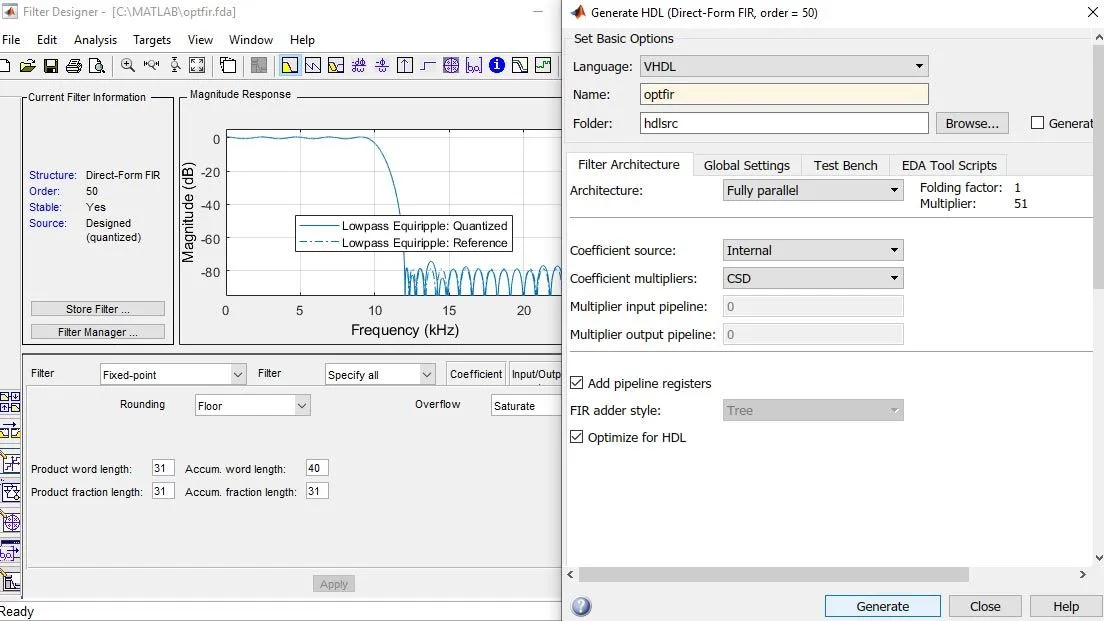

Filter Design HDL Coder generates synthesizable, portable VHDL® and Verilog® code for implementing fixed-point filters designed with MATLAB on FPGAs or ASICs.

Vendor

MathWorks Inc.

Company Website

It automatically creates VHDL and Verilog test benches for simulating, testing, and verifying the generated code.

Get Started:

- Working with Filter Design HDL Coder

- Designing Fixed-Point Filters

- Optimizing Filter Architecture

- Generating HDL for Fixed-Point Filters

- Customizing VHDL and Verilog Code

- Testing and Synthesizing Generated HDL Code

Filter Design HDL Coder is integrated with DSP System Toolbox to provide a unified design and implementation environment. You can design filters and generate VHDL and Verilog code either from the MATLAB command line or from DSP System Toolbox using the Filter Designer app or the Filter Builder app.

The design entry input to Filter Design HDL Coder is a quantized filter that you create in one of two ways:

- Design and quantize the filter with DSP System Toolbox

- Design the filter with Signal Processing Toolbox and then quantize it with DSP System Toolbox

Filter Design HDL Coder supports several important filter structures, including: Discrete-time finite impulse response (FIR), which includes symmetric, anti-symmetric, and transposed structures Second-order section (SOS) infinite impulse response (IIR), which includes direct form I, II, and transposed structures Multirate filters, which includes cascaded integrator-comb (CIC) interpolator and decimator, direct-form FIR and transposed FIR polyphase interpolator and decimator, FIR hold and linear interpolator, and FIR polyphase sample rate converter structures Fractional delay filters, which includes Farrow structures Filter Design HDL Coder can generate HDL code from cascaded multirate and discrete-time filters. Each of these single-rate and multirate filter structures supports fixed-point and floating-point (double precision) realizations. In addition, the FIR structures support unsigned fixed-point coefficients.